Abstract

Solder based flip-chip packaging has prompted interest in many integrated circuit (IC)packaging applications due to its many advantages in terms of cost, package size, electricalperformance, input/output density, etc. The ball grid array (BGA) is one of the most commonflip-chip packaging techniques used for microprocessor applications. However, mechanicalstresses induced by the flip-chip process can impact adversely on the reliability of production.

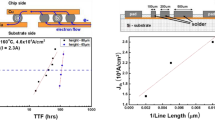

White beam synchrotron x-ray topography (SXRT), a non-destructive technique, has beenemployed to investigate the spatial extent of strain fields imposed on the underlying siliconsubstrate for Intelν®Pentiumν®III microprocessors due to the lead-tin solder bump process for BGApackaging. Large area and section back-reflection SXRT images were taken before and after asimulation of the reflow process at 350°C in atmosphere. The presence of induced strain fields inthe Si substrate due to the overlying bump structures has been observed via the extinction contrasteffect in these x-ray topographs. In addition, orientational contrast effects have also been foundafter the reflow process due to the severe stresses in the underlying silicon beneath the lead bumps.The estimated magnitudes of stress, ∣σ∣, imposed on the underlying silicon were calculated to be100 MPa. The spatial strains in the underlying silicon were relieved dramatically after the leadbumps were removed from the wafer, which confirms that the bumps are indeed a major source ofstrain in the underlying Si. Finite element analysis (FEA) has also been performed in 2-D planestrain mode. The magnitudes and spatial distribution of the stresses after the reflow process are ingood agreement with the SXRT results.

Similar content being viewed by others

References

G.R. Blackwell, Chapter 4: Direct Chip Attach, The Electronic Packaging Handbook, ed. G.R. Blackwell (CRC Press, 1999).

V.K. Nagesh, R. Peddada, S. Ramalingam, B. Sur and A. Tai, Challenges of Flip Chip on Organic substrateAssembly Technology, IEEE Proceeding 1999 Electronics Component and technology conference, pp.975–978 (1999).

P.J. McNally, J. Curley, M. Bolt, A. Reader, T. Tuomi, R. Rantamaki, A. Danilewsky and I. De wolf, Monitoring of Stress Reduction in Shallow Trench Isolation CMOS structures Via Synchrotron X-rayTopography, Electrical Data and Raman Spectroscopy, Journal of Materials Science: Materials in Electronics 10, pp.351–358 (1999).

J. Wang, Z. Qian and S. Liu, Process Induced Stresses of a Flip-Chip Packaging by Sequential ProcessingModeling Technique, Transactions of the ASME, Journal of Electronic Packaging 120, pp.309–313 (1998).

Q. Yao and J. Qu, Three-Dimensional Versus Two-Dimensional Finite Element Modeling of Flip-ChipPackages, Transactions of the ASME, Journal of Electronic Packaging 121, pp.196–201 (1999).

M.N. Variyam, W. Xie and S.K. Sitaraman, Role of Out-of-Plane Coefficient of Thermal Expansion inElectronic Packaging Modeling, Transactions of the ASME, Journal of Electronic Packaging 122, pp.121–127 (2000).

T. Tuomi, K. Naukkarinen and P. Rabe, Use of Synchrotron Radiation in X-ray Diffraction Topography, Phys. Stat. Sol. A 25, pp.93–106 (1974).

P.J. McNally, J. Curley, A. Krier, Y. Mao, J. Richardson, T. Tuomi, M. Taskinen, R. Rantamaki, E. Prieurand A. Danilewsky, An Evaluation of Liquid Phase Epitaxial InGaAs/InAs Heterostructures for InfraredDevices Using Synchrotron X-ray Topography, Semiconductor Science and Technology 13, pp.345–349 (1998).

R. Rantamaki, X-ray Topography of Semiconductors using Synchrotron Radiation, HD. Sci Thesis, Optoelectronics Laboratory, Department of Electrical and Communications Engineering, HelsinkiUniversity of Technology, pp.11–12 (1999).

A. Brand, A. Haranahalli, N. Hsieh, Y.C. Lin, G. Sery, N. Stenton, B.J. Woo, S. Ahmed, M. Bohr, S. Yang, “Intel’s 0.25 Micron, 2.0 Volts Logic Process Technology”, Intel Technology Journal, 3rd Quarter 1998.http://developer.intel.com/technology/itj/q31998

E.S. Meieran and I.A. Blech, X-ray Extinction Contrast Topography of Silicon Strained by Thin SurfaceFilms, Journal of Applied Physics 36, pp.3162–3167 (1965).

M. Karilahti, T. Tuomi, M. Taskinen, J. Tulkki, H. Lipsanen and P. McNally, Synchrotron X-rayTopographic Study of Strain in Silicon Wafers with Intergrated Circuits, IL Nuovo Cimento, 19D(2-4), pp.181–184 (1997).

J.A. King, Materials, Handbook for Hybrid Microelectronics (Artech, USA, 1988).

Quickfield™, www.quickfield.com

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Kanatharana, J., Pérez-Camacho, J.J., Buckley, T. et al. Investigation of Mechanical Stresses in Underlying Silicon due to Lead-Tin Solder Bumps via Synchrotron X-Ray Topography and Finite Element Analysis. MRS Online Proceedings Library 682, 57 (2001). https://doi.org/10.1557/PROC-682-N5.7

Published:

DOI: https://doi.org/10.1557/PROC-682-N5.7